Short Bio:

Georgios Zervakis received the Diploma and Ph.D. degrees from the School of Electrical and Computer Engineering (ECE), National Technical University of Athens (NTUA), Greece, in 2012 and 2018, respectively. He is currently a research assistant and group leader at the Chair for Embedded Systems (CES), at the Karlsruhe Institute of Technology (KIT). Before joining KIT, he was a postdoctoral research fellow at Microprocessors Laboratory and Digital Systems Lab (Microlab), ECE, NTUA. In addition, he has worked as a research associate at the Aristotle University of Thessaloniki (AUTH), the National and Kapodistrian University of Athens (UOA), and as a principal investigator at the Institute of Communication and Computer Systems (ICCS), Greece. As a member of ICCS, he worked in several European projects including among others the AEGLE, FABSPACE 2.0, and EXA2PRO.

Research Interests:

- Approximate computing

- Design automation and synthesis

- Neural Network accelerators

- Hardware acceleration in cloud

Publications

| Journals | |

|---|---|

| Dimitrios Danopoulos, Georgios Zervakis, Dimitrios Soudris, Jörg Henkel TransAxx: Efficient Transformers with Approximate Computing in IEEE Transactions on Circuits and Systems for Artificial Intelligence ( Volume 2, Issue 4), DOI, PDF, Dec 2025. | |

| Argyris Kokkinis; Georgios Zervakis; Kostas Siozios; Mehdi Baradaran Tahoori; Jörg Henkel Enabling Printed Multilayer Perceptrons Realization via Area-Aware Neural Minimization in IEEE Transactions on Computers ( Volume 74, Issue 4), DOI, PDF, Apr 2025. | |

| Georgios Zervakis, Fabio Frustaci, Ourania Spantidi, Iraklis Anagnostopoulos, Hussam Amrouch, Jörg Henkel Leveraging Highly Approximated Multipliers in DNN Inference in IEEE Access (Volume 13), DOI, PDF, Mar 2025. | |

| Konstantinos Balaskas, Andreas Karatzas, Christos Sad, Kostas Siozios, Iraklis Anagnostopoulos, Georgios Zervakis, Jörg Henkel Hardware-Aware DNN Compression via Diverse Pruning and Mixed-Precision Quantization in IEEE Transactions on Emerging Topics in Computing (Volume 12, Issue 4), DOI, PDF, Dec 2024. | |

| Giorgos Armeniakos, Georgios Zervakis, Dimitrios Soudris, Mehdi B. Tahoori, and Jörg Henkel Model-to-Circuit Cross-Approximation For Printed Machine Learning Classifiers in Transactions on Computer-Aided Design of Integrated Circuits (Volume 42, Issue 11), DOI, PDF, Nov 2023. | |

| Giorgios Armeniakos, Georgios Zervakis, Dimitrios Soudris, Mehdi Tahoori, Jörg Henkel Co-Design of Approximate Multilayer Perceptron for Ultra-Resource Constrained Printed Circuits in Transactions on Computers (Volume 72, Issue 9), DOI, PDF, Sep 2023. | |

| Dimitrios Danopoulos, Georgios Zervakis, Kostas Siozios, Dimitrios Soudris and Jörg Henkel AdaPT: Fast Emulation of Approximate DNN Accelerators in PyTorch in Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD Volume 42, Issue 6), DOI, PDF, Jun 2023. Sourcecode on github | |

| Giorgos Armeniakos, Georgios Zervakis, Dimitrios Soudris, Jörg Henkel Hardware Approximate Techniques for Deep Neural Network Accelerators: A Survey in ACM Computing Surveys (CSUR, Volume 55, Issue 4), DOI, PDF, Apr 2023. | |

| Ourania Spantidi, Georgios Zervakis, Sami Alsalamin, Isai Roman-Ballesteros, Jörg Henkel, Hussam Amrouch, and Iraklis Anagnostopoulos Targeting DNN Inference via Efficient Utilization of Heterogeneous Precision DNN Accelerators in IEEE Transactions on Emerging Topics in Computing (Volume 11, Issue 1), DOI, PDF, Mar 2023. | |

| Ourania Spantidi, Georgios Zervakis, Iraklis Anagnostopoulos, and Jörg

Henkel Energy-efficient DNN Inference on Approximate Accelerators Through Formal Property Exploration in IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD, Volume 41, Issue 11), DOI, PDF, Nov 2022. | |

| Konstantinos Balaskas, Florian Klemme, Georgios Zervakis, Kostas Siozios, Hussam Amrouch, Jörg Henkel Variability-Aware Approximate Circuit Synthesis via Genetic Optimization in IEEE Transactions on Circuits and Systems I: Regular Papers (Volume 69, Issue 10), DOI, PDF, Oct 2022. | |

| Georgios Zervakis, Iraklis Anagnostopoulos, Sami Alsalamin, Ourania Spantidi, Isai Roman-Ballesteros, Jörg Henkel, Hussam Amrouch Thermal-Aware Design for Approximate DNN Accelerators in IEEE Transactions on Computers (Volume 71, Issue 10), DOI, PDF, Oct 2022. | |

| S. Salamin, G. Zervakis, F. Klemme, H. Kattan, Y. Chauhan, J. Henkel, and H. Amrouch Impact of NCFET Technology on Eliminating the Cooling Cost and Boosting the Efficiency of Google TPU in IEEE Transactions on Computers (Volume 71, Issue 4), DOI, PDF, Apr 2022. | |

| Nafis Irtija, Iraklis Anagnostopoulos, Georgios Zervakis, Eirini Eleni Tsiropoulou, Hussam Amrouch, Jörg Henkel Energy Efficient Edge Computing Enabled by Satisfaction Games and Approximate Computing in IEEE Transactions on Green Communications and Networking (Volume 6, Issue 1), DOI, PDF, Mar 2022. | |

| Konstantinos Balaskas, Georgios Zervakis, Hussam Amrouch, Jörg Henkel, Kostas Siozios Automated Design Approximation to Overcome Circuit Aging in IEEE Transactions on Circuits and Systems I: Regular Papers (Volume 68, Issue 11), DOI, PDF, Nov 2021. | |

| Sami Salamin, Georgios Zervakis, Yogesh Singh Chauhan, Jörg Henkel, Hussam Amrouch PROTON: Post-Synthesis Ferroelectric Thickness Optimization for NCFET Circuits in IEEE Transactions on Circuits and Systems I: Regular Papers (Volume 68, Issue 10), DOI, PDF, Oct 2021. | |

| Georgios Zervakis, Iraklis Anagnostopoulos, Sami Salamin, Yogesh S. Chauhan, Jörg Henkel, Hussam Amrouch Impact of NCFET on Neural Network Accelerators in IEEE Access (Volume 9), DOI, PDF, Mar 2021. | |

| Guilherme Paim, Georgios Zervakis, Girish Pahwa, Yogesh S. Chauhan,

Eduardo A. C. da Costa, Sergio Bampi, Jörg Henkel, and Hussam Amrouch On the Resiliency of NCFET Circuits against Voltage Over-Scaling in IEEE Transactions on Circuits and Systems I: Regular Papers (Volume 68, Issue 4), DOI, PDF, Mar 2021. | |

| Hussam Amrouch, Georgios Zervakis, Sami Salamin, Hammam Kattan, Iraklis Anagnostopoulos and Jörg Henkel NPU Thermal Management in IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD), ESWEEK Special Issue (Volume 39, Issue 11), DOI, PDF, Nov 2020. | |

| Zois-Gerasimos Tasoulas, Georgios Zervakis, Iraklis Anagnostopoulos, Hussam Amrouch, Jörg Henkel Weight-Oriented Approximation for Energy-Efficient Neural Network Inference Accelerators in IEEE Transactions on Circuits and Systems I: Regular Papers (Volume 67, Issue 12), DOI, PDF, Sep 2020. | |

| Georgios Zervakis, Hussam Amrouch and Jörg Henkel Design Automation of Approximate Circuits With Runtime Reconfigurable Accuracy in IEEE Access (Volume 8), DOI, PDF, Mar 2020. |

| Conferences | |

|---|---|

| Georgios Mentzos, Valentin Alexander Frey, Konstantinos Balaskas, Georgios Zervakis and Jörg Henkel R2T-Tiny: Runtime-Reconfigurable Throughput-Optimized TinyML for Hybrid Inference Acceleration on FPGA SoCs in International Conference on Computer-Aided Design (ICCAD), Oct 26 - 30 2025. | |

| Ourania Spantidi; Georgios Zervakis; Jörg Henkel; Iraklis Anagnostopoulos

Approximate Multiplier Mapping for Unfairness Mitigation in Energy-Efficient DNNs in 2025 IEEE International Symposium on Circuits and Systems (ISCAS), DOI, PDF, May 25 - 28 2025. | |

| Argyris Kokkinis, Georgios Zervakis, Kostas Siozios, Mehdi B. Tahoori, Jörg

Henkel Hardware-Aware Automated Neural Minimization for Printed Multilayer Perceptrons in 26th Design, Automation and Test in Europe Conference (DATE'23), Antwerp, Belgium, DOI, PDF, Apr 17-19 2023. | |

| Jörg Henkel, Hai Li, Anand Raghunathan, Mehdi B. Tahoori, Swagath Venkataramani, Xiaoxuan Yang, Georgios Zervakis Approximate Computing and the Efficient Machine Learning Expedition (invited) in IEEE/ACM International Conference on Computer-Aided Design (ICCAD '22), DOI, PDF, Oct 30 - Nov 03 2022. | |

| Konstantinos Balaskas, Georgios Zervakis, Kostas Siozios, Mehdi B. Tahoori, Jörg Henkel Approximate Decision Trees For Machine Learning Classification on Tiny Printed Circuits in 23rd International Symposium on Quality Electronic Design (ISQED '22), DOI, PDF, 6-8 April 2022. |   |

| Giorgos Armeniakos, Georgios Zervakis, Dimitrios Soudris, Mehdi B. Tahoori, Jörg Henkel Cross-Layer Approximation For Printed Machine Learning Circuits in IEEE/ACM 25th Design, Automation and Test in Europe Conference (DATE'22), Antwerp, Belgium, DOI, PDF, Mar 14-23 2022. Best Paper Nomination |   |

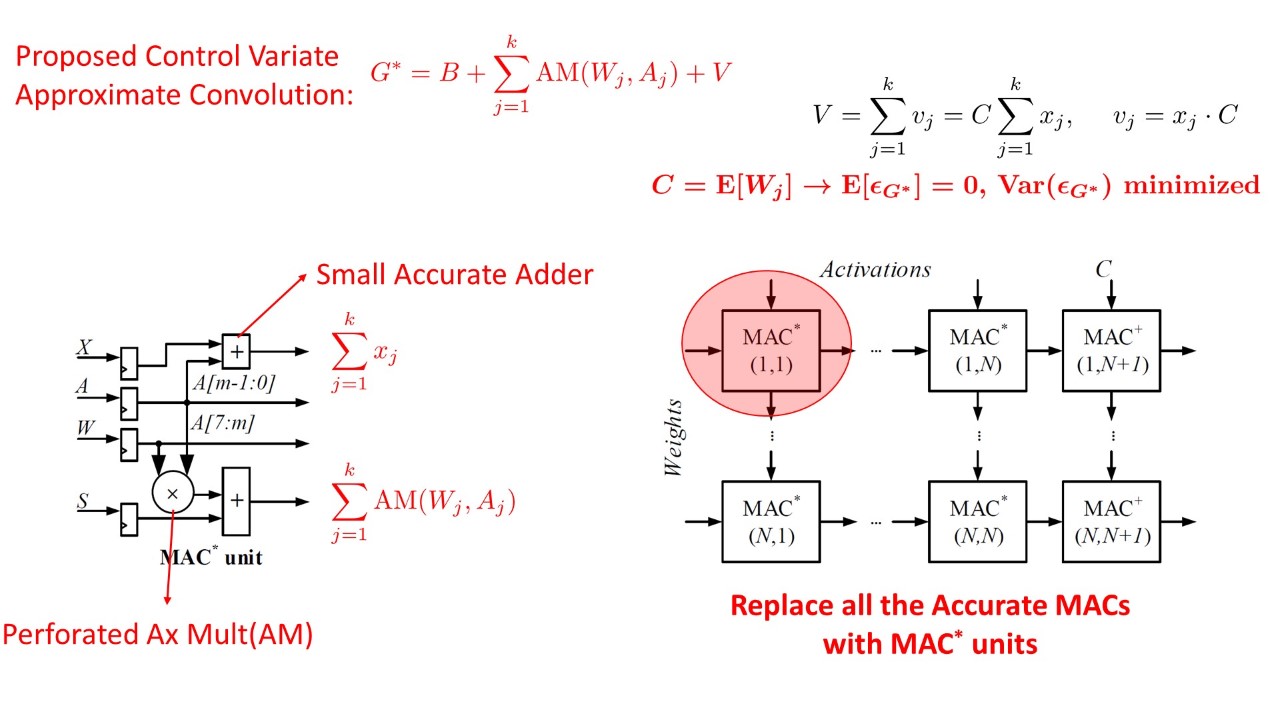

| G. Zervakis, O. Spantidi, I. Anagnostopoulos, H. Amrouch, and J. Henkel Control Variate Approximation for DNN Accelerators in 58th Design Automation Conference (DAC), San Francisco, DOI, PDF, Dec 5-9 2021. |   |

| Ourania Spantidi, Georgios Zervakis, Iraklis Anagnostopoulos, Hussam

Amrouch, and Jörg Henkel Positive/Negative Approximate Multipliers for DNN Accelerators in IEEE/ACM 40th International Conference On Computer Aided Design (ICCAD), Virtual Conference, DOI, PDF, Nov 1-5 2021. |   |

| Mikail Yayla, Kuan-Hsun Chen, Georgios Zervakis, Jörg Henkel, Jian-Jia

Chen, and Hussam Amrouch FeFET and NCFET for Future Neural Networks: Visions and Opportunities (special session) in 24th Design, Automation and Test in Europe Conference (DATE'21), Virtual Conference, DOI, PDF, Feb 1-5 2021. | |

| Sami Salamin, Georgios Zervakis, Ourania Spantidi, Iraklis

Anagnostopoulos, Jörg Henkel and Hussam Amrouch Reliability-Aware Quantization for Anti-Aging NPUs in IEEE/ACM 24th Design, Automation and Test in Europe Conference (DATE'21), Virtual Conference, DOI, PDF, Feb 1-5 2021. | |

| Georgios Zervakis, Hassaan Saadat, Hussam Amrouch, Andreas Gerstlauer,

Sri Parameswaran, and Jörg Henkel Approximate Computing for ML: State-of-the-art, Challenges and Visions (special session) in 26th Asia and South Pacific Design Automation Conference (ASPDAC ’21), DOI, PDF, Jan 18-21 2021. | |

| Georgios Mentzos, Konstantinos Balaskas, Georgios Zervakis and Jörg Henkel Late-Breaking Results: Ultra Energy Efficient Personalized Glucose Prediction with RLS Implementation on a Tiny FPGA , 2026. | |

| Georgios Mentzos, Konstantinos Balaskas, Georgios Zervakis and Jörg Henkel Late Breaking Results: Towards Low-Latency TinyML via Regularized Activation Packing , 2026. | |

| arXiv | |

|---|---|

| Dimitrios Danopoulos, Georgios Zervakis, Dimitrios Soudris, Jörg Henkel TransAxx: Efficient Transformers with Approximate Computing in arxiv, DOI, PDF, 2024. | |

| Argyris Kokkinis, Georgios Zervakis, Kostas Siozios, Mehdi B. Tahoori, Jörg Henkel Hardware-Aware Automated Neural Minimization for Printed Multilayer Perceptrons in arXiv, DOI, PDF, Jan 2023. | |

| Dimitrios Danopoulos, Georgios Zervakis, Kostas Siozios, Dimitrios Soudris and Jörg Henkel AdaPT: Fast Emulation of Approximate DNN Accelerators in PyTorch in arXiv, DOI, PDF, Mar 2022. |

| Books / Book Chapter | |

|---|---|

| Georgios Zervakis, Iraklis Anagnostopoulos, Hussam Amrouch, and Jörg

Henkel Enabling Efficient Inference of Convolutional Neural Networks via Approximation In: Liu, W., Lombardi, F. (eds) Approximate Computing. Springer, Cham., DOI, PDF, 2022. ISBN: 978-3-030-98346-8 |

Previous publications

| Journals |

|---|

| G. Zervakis, K. Koliogeorgi, D. Anagnostos, N. Zompakis, and K. Siozios VADER: VoltageDriven Netlist Pruning for CrossLayer Approximate Arithmetic Circuits in IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 27, no. 6, pp. 1460–1464, DOI, Jun. 2019. |

| G. Zervakis, S. Xydis, D. Soudris, and K. Pekmestzi, MultiLevel Approximate Accelerator Synthesis Under Voltage Island Constraints in IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 66, no. 4, pp. 607–611, DOI, Apr. 2019. |

| V. Leon, G. Zervakis, S. Xydis, D. Soudris, and K. Pekmestzi Walking through the EnergyError Pareto Frontier of Approximate Multipliers in IEEE Micro, vol. 38, no. 4, pp. 40–49, DOI, Jul. 2018. |

| G. Zervakis, F. Ntouskas, S. Xydis, D. Soudris, and K. Pekmestzi VOSsim: A Framework for Enabling Fast Voltage Overscaling Simulation for Approximate Computing Circuits in IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 26, no. 6, pp. 1204–1208, DOI, Jun. 2018. |

| V. Leon, G. Zervakis, D. Soudris, and K. Pekmestzi Approximate Hybrid High Radix Encoding for EnergyEfficient Inexact Multipliers in IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 26, no. 3, pp. 421–430, DOI, Mar. 2018. |

| G. Zervakis, K. Tsoumanis, S. Xydis, D. Soudris, and K. Pekmestzi DesignEfficient Approximate Multiplication Circuits Through Partial Product Perforation in IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 24, no. 10, pp. 3105–3117, DOI, Oct. 2016. |

| K. Tsoumanis, N. Axelos, N. Moschopoulos, G. Zervakis, and K. Pekmestzi PreEncoded Multipliers Based on NonRedundant Radix4 SignedDigit Encoding in IEEE Transactions on Computers, vol. 65, no. 2, pp. 670–676, DOI, Feb. 2016. |

| K. Tsoumanis, S. Xydis, G. Zervakis, and K. Pekmestzi Flexible DSP Accelerator Architecture Exploiting CarrySave Arithmetic in IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 24, no. 1, pp. 368–372, DOI, Jan. 2016. |

| Conferences |

|---|

| K. Koliogeorgi, G. Zervakis, D. Anagnostos, N. Zompakis, and K. Siozios Optimizing SVM Classifier Through Approximate and High Level Synthesis Techniques in 2019 8th International Conference on Modern Circuits and Systems Technologies (MOCAST), IEEE, 2019, pp. 1–4. DOI. |

| D. Masouros, K. Koliogeorgi, G. Zervakis, A. Kosvyra, A. Chytas, S. Xydis, I. Chouvarda, and D. Soudris Codesign implications of costeffective ondemand acceleration for cloud healthcare analytics: The aegle approach in 2019 Design, Automation Test in Europe Conference Exhibition (DATE), 2019, pp. 622–625. DOI. |

| N. Zompakis, D. Anagnostos, K. Koliogeorgi, G. Zervakis, and K. Siozios A Design Flow Framework for FullyConnected Neural Networks Rapid Prototyping in Proceedings of the International Conference on OmniLayer Intelligent Systems, ACM, 2019, pp. 44–49. DOI:. |

| K. Koliogeorgi, D. Masouros, G. Zervakis, S. Xydis, T. Becker, G. Gaydadjiev, and D. Soudris AEGLE’s Cloud Infrastructure for Resource Monitoring and Containerized Accelerated Analytics in 2017 IEEE Computer Society Annual Symposium on VLSI (ISVLSI), Jul. 2017, pp. 362–367. DOI. |

| G. Zervakis, S. Xydis, and D. Soudris Performancepower exploration of softwaredefined big data analytics: The AEGLE cloud backend in 2016 International Conference on Embedded Computer Systems: Architectures, Modeling and Simulation (SAMOS), IEEE, Jul. 2016, pp. 312–319. DOI. |

| N. Eftaxiopoulos, N. Axelos, G. Zervakis, K. Tsoumanis, and K. Pekmestzi Delta DICE: A Double Node Upset resilient latch in 2015 IEEE 58th International Midwest Symposium on Circuits and Systems (MWSCAS), Aug. 2015, pp. 1–4. DOI. |

| G. Zervakis, S. Xydis, K. Tsoumanis, D. Soudris, and K. Pekmestzi Hybrid approximate multiplier architectures for improved poweraccuracy tradeoffs in 2015 IEEE/ACM International Symposium on Low Power Electronics and Design (ISLPED), Jul. 2015, pp. 79–84. DOI. |

| G. Zervakis, K. Tsoumanis, S. Xydis, N. Axelos, and K. Pekmestzi Approximate Multiplier Architectures Through Partial Product Perforation: PowerArea Tradeoffs Analysis in Proceedings of the 25th Edition on Great Lakes Symposium on VLSI (GLSVLSI), ACM, 2015, pp. 229–232. DOI. |

| N. Eftaxiopoulos, N. Axelos, G. Zervakis, K. Tsoumanis, and K. Pekmestzi An independent dual gate SOI FinFET softerror resilient memory cell in 2014 9th International Design and Test Symposium (IDT), IEEE, Dec. 2014, pp. 39–44. DOI. |

| N. Eftaxiopoulos, G. Zervakis, K. Pekmestzi, and C. Efstathiou High performance MAC designs in 2014 9th International Design and Test Symposium (IDT), IEEE, Dec. 2014, pp. 30–35. DOI. |

| G. Zervakis, N. Eftaxiopoulos, K. Tsoumanis, N. Axelos, and K. Pekmestzi A high radix montgomery multiplier with concurrent error detection in 2014 9th International Design and Test Symposium (IDT), IEEE, Dec. 2014, pp. 199–204. DOI. |

| N. Axelos, N. Eftaxiopoulos, G. Zervakis, K. Tsoumanis, and K. Pekmestzi FFDICE: An 8T softerror tolerant cell using Independent Dual Gate SOI FinFETs in 2014 IEEE 20th International OnLine Testing Symposium (IOLTS), Jul. 2014, pp. 200–201. DOI. |

| G. Zervakis, N. Eftaxiopoulos, K. Tsoumanis, N. Axelos, and K. Pekmestzi A segmentationbased BISR scheme in 2014 19th Asia and South Pacific Design Automation Conference (ASPDAC), Jan. 2014, pp. 652–657. DOI. |

| N. EftaxiopoulosSarris, G. Zervakis, K. Tsoumanis, and K. Pekrnestzi A radiation tolerant and selfrepair memory cell in 2013 IEEE 19th International OnLine Testing Symposium (IOLTS), Jul. 2013, pp. 210–215. DOI. |

| Book Chapters |

|---|

| C. Kachris, E. Koromilas, I. Stamelos, G. Zervakis, S. Xydis, and D. Soudris EnergyEfficient Acceleration of Spark Machine Learning Applications on FPGAs C. Kachris, B. Falsafi, and D. Soudris, Eds. Cham: Springer International Publishing, 2019, pp. 87–107. DOI. |

| G. Zervakis On Accelerating Data Analytics: An Introduction to the Approximate Computing Technique K. Siozios, D. Anagnostos, D. Soudris, and E. Kosmatopoulos, Eds. Cham: Springer International Publishing, 2019, pp. 163–180. DOI. |

Student Theses

| Name | Type of work | Title | Mentor | Completion date |

|---|---|---|---|---|

| Giakoumidakis, Nikolaos | Bachelor thesis | approximate Multi Layer Perceptron | Zervakis, Georgios | 2022-12-31 |

| Balaskas, Konstantinos | Master thesis | Approximate Computing | Amrouch, Hussam / Zervakis, Georgios | 2021-09-30 |

| Roman Ballesteros, Isai | Internship | Deep Neural Network | Amrouch, Hussam / Zervakis, Georgios | 2020-12-31 |

| Abdelhamid, Mohamed | Bachelor thesis | Machine Learning | Amrouch, Hussam / Zervakis, Georgios | 2020-07-31 |

| El-Sherif, Ahmed | Bachelor thesis | Reliability-Aware Circuit Design | Amrouch, Hussam / Zervakis, Georgios | 2020-07-31 |

| Elfeky, Lujine | Bachelor thesis | Machine Learning | Amrouch, Hussam / Zervakis, Georgios | 2020-07-31 |