Low Power Design and Embedded Systems

- type: Praktikum (P)

- chair: KIT Department of Informatics

- semester: SS 2026

-

lecturer:

Prof. Dr.-Ing. Jörg Henkel

Dr.-Ing. Heba Khdr

Dr.-Ing. Mohammed Bakr Sikal

Georgios Mentzos - SWS: 4

- ECTS: 4

- lv-no.: 2424811

- information: Blended (On-Site/Online)

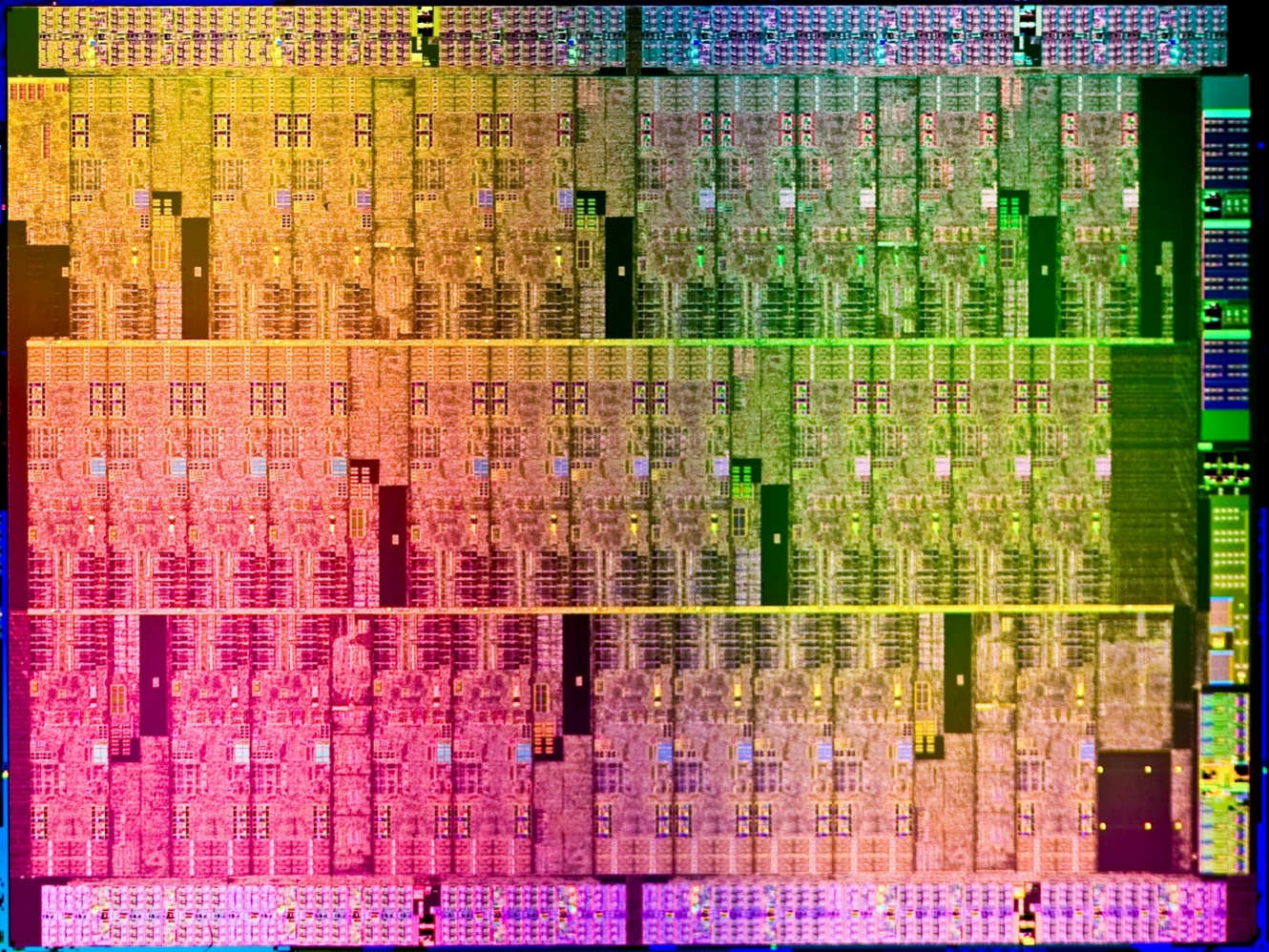

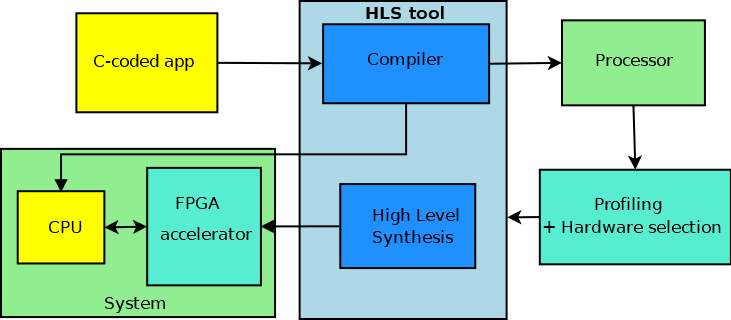

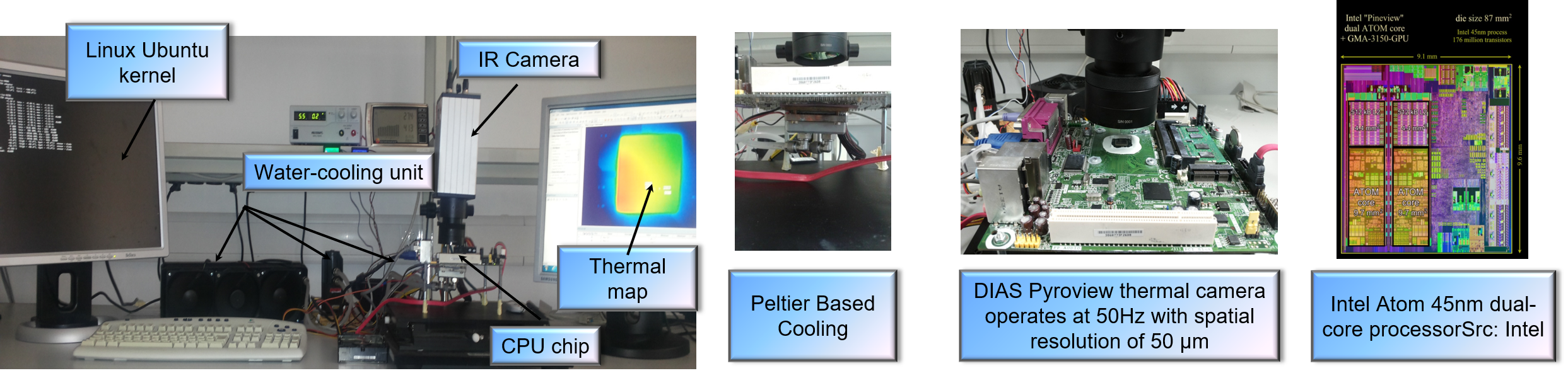

| Content | Lab Description Nowadays, power and energy consumption are two of the most important criteria in the design of on-chip applications. Other design constraints, such as performance, were dominant in the past, but now it is imperative to optimize for low power, since on-chip temperature and battery life are limiting design factors on modern multi / many core systems. First part: software effects on power and performance The first part of the lab consists of an exploration and analysis of the effect of different resource management techniques on a many-core platform, to optimize for a specific metric (e.g. energy, power, temperature) under predefined application constraints (e.g. performance). Second part: hardware / software co-design The second part of the lab consists of a Hardware/Software Co-design exploration using the High-Level Synthesis (HLS) technique. This technique takes a C/C++ code implementation and produces a hardware accelerator module from a function, which is then synthesized for a Field Programable Gate Array (FPGA) device. Third Part: Demo in Thermal Lab As part of the course, there will be access to the CES thermal lab, in which an experiment will be carried out to analyze the effect of power and temperature on a real board setup, using a thermal camera. Preliminary discussion appointment: it will be announced via email to all registrants. |

| Language of instruction | English |

| Lab Description Nowadays, power and energy consumption are two of the most important criterions in the design of on-chip applications. Other design constraints, such as performance, were dominant in the past, but now it is imperative to optimize for low power, since on-chip temperature and battery life are limiting design factors on modern multi/many core systems. This lab explores different software and hardware approaches for power and energy reduction on modern embedded systems, considering other relevant metrics and constraints (e.g., temperature, performance, chip area). |

|

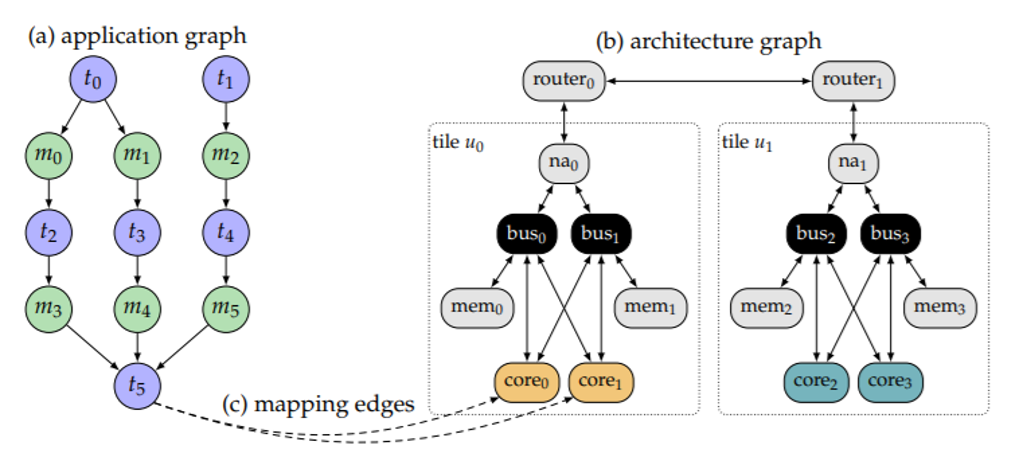

| First Part: Power and Thermal-aware Resource Management The first part of the lab consists of an exploration and analysis of the effect of different resource management techniques on a many-core platform, to optimize for a specific metric (e.g. energy, power, temperature) under predefined application constraints (e.g. performance). |

|

| Second Part: Hardware/Software Co-design The second part of the lab consists of a Hardware/Software Co-design exploration using the High-Level Synthesis (HLS) technique. This technique takes a C code implementation and produces three types of system implementation: a complete hardware (RTL) implementation, a pure software implementation to be executed in a MIPS soft-processor, and a hybrid implementation where one or more functions of a program are compiled to hardware accelerators with the remaining program segments running in software in a MIPS soft-processor. |

|

| Third Part: Demo in Thermal Lab As part of the course, there will be access to the CES thermal lab, in which an experiment will be carried out to analyse the effect of power and temperature on a real board setup, using a thermal camera. |

|